# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## **19ECB302–VLSI DESIGN**

III YEAR/ V SEMESTER

**UNIT 1 – MOS TRANSISTOR PRINCIPLE**

**TOPIC 8 – STICK DIAGRAM**

### **OUTLINE**

- INTRODUCTION

- CMOS INVERTER

- MAPPING:STICK DIAGRAM -> CMOS TRANSISTOR CIRCUIT

- NMOS INVERTER-STICK DIAGRAM

- STATIC CMOS NAND GATE

- STATIC CMOS NOR GATE

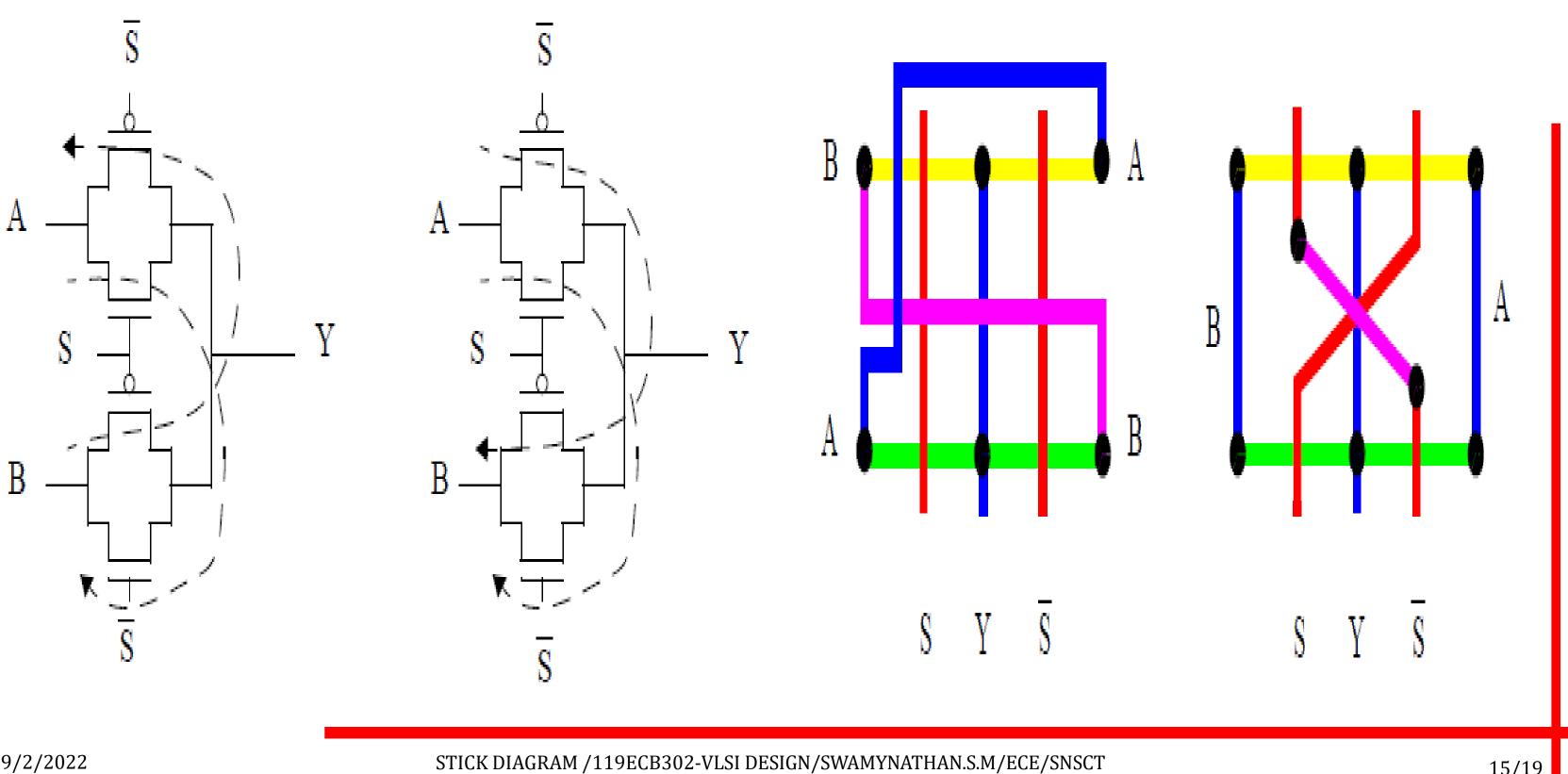

- STATIC CMOS EXAMPLES-2 STYLES

- ACTIVITY

- EULER PATH

- YOUTUBE VIDEO

- ASSESSMENT

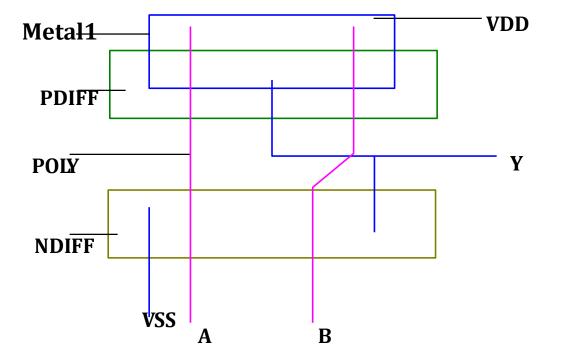

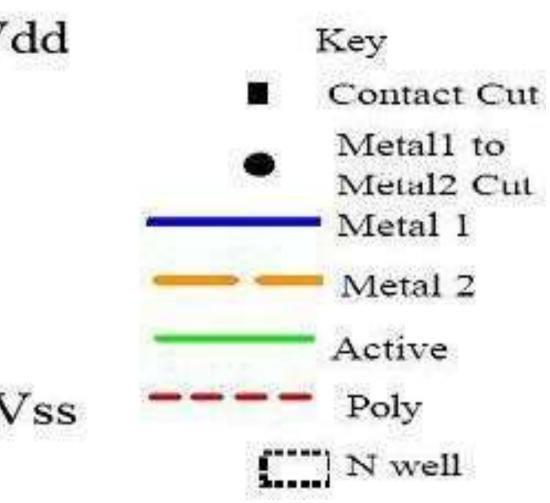

### **STICK DIAGRAMS-INTRODUCTION**

- Intermediate representation between circuit diagram and layout

- •Symbolic design is "Sticks" layout.

- •Metal-wire

- •VDD-power supply

- •POLY-Polysilicon (Gate)

- •NDIFF-N diffusion(Source)

- PDIFF-P diffusion(Drain)

- •VSS-Ground

- •A,B-Input

- •Y-Output

# Symbol and Stick Diagram of 2 inputs NAND gate

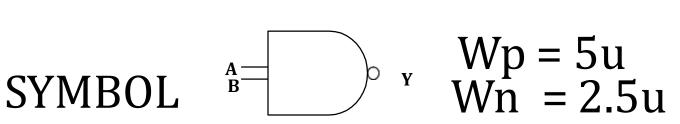

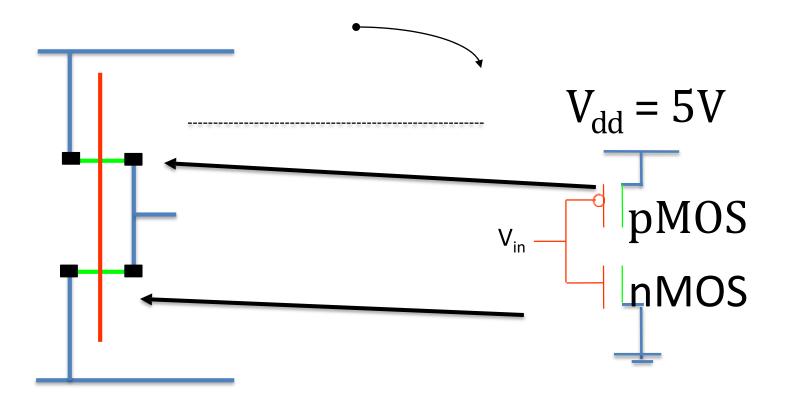

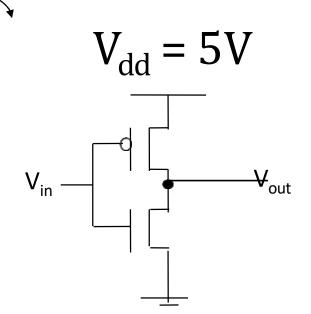

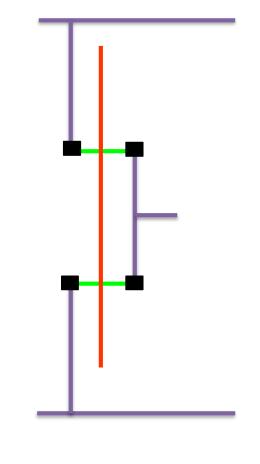

### **CMOS INVERTER STICK DIAGRAM**

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

9/2/2022

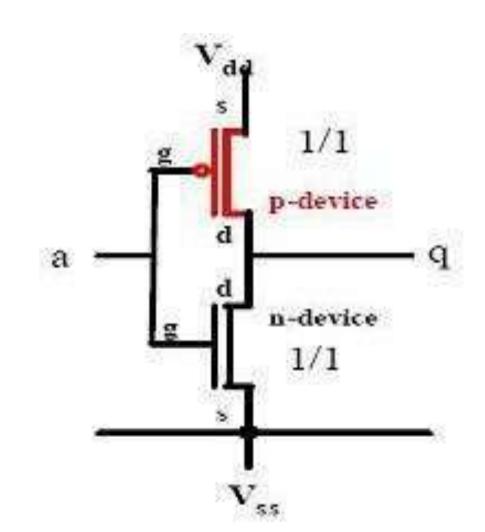

### **MAPPING:STICK DIAGRAM -> CMOS TRANSISTOR CIRCUIT**

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

9/2/2022

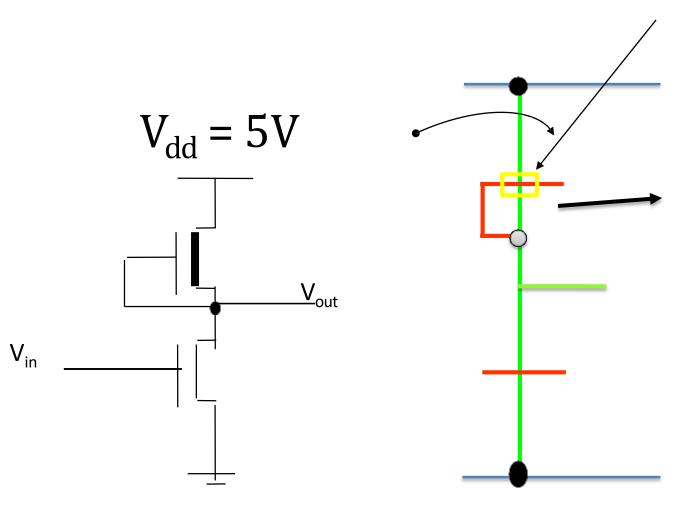

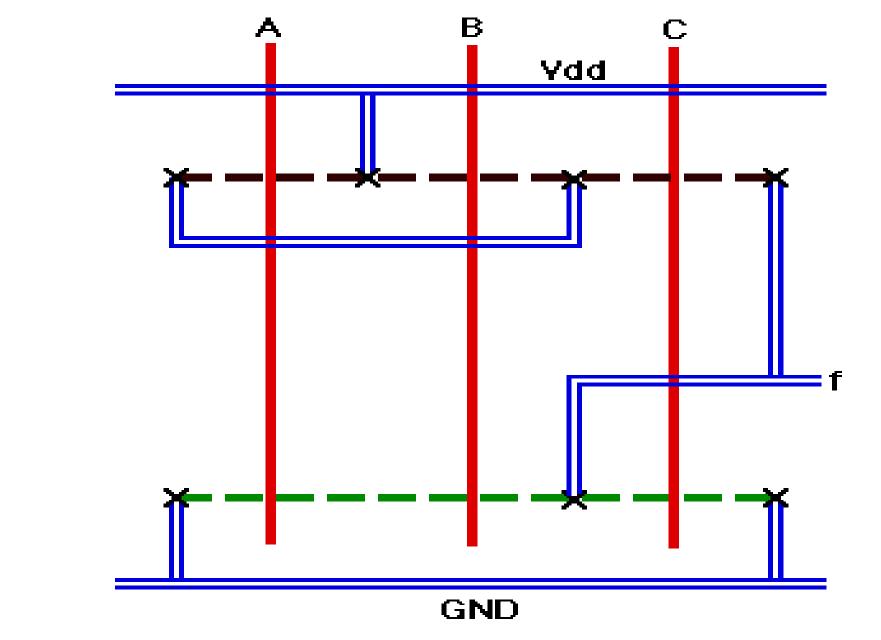

### **NMOS INVERTER COLOURED STICK DIAGRAM**

9/2/2022

### \* Note the depletion mode device

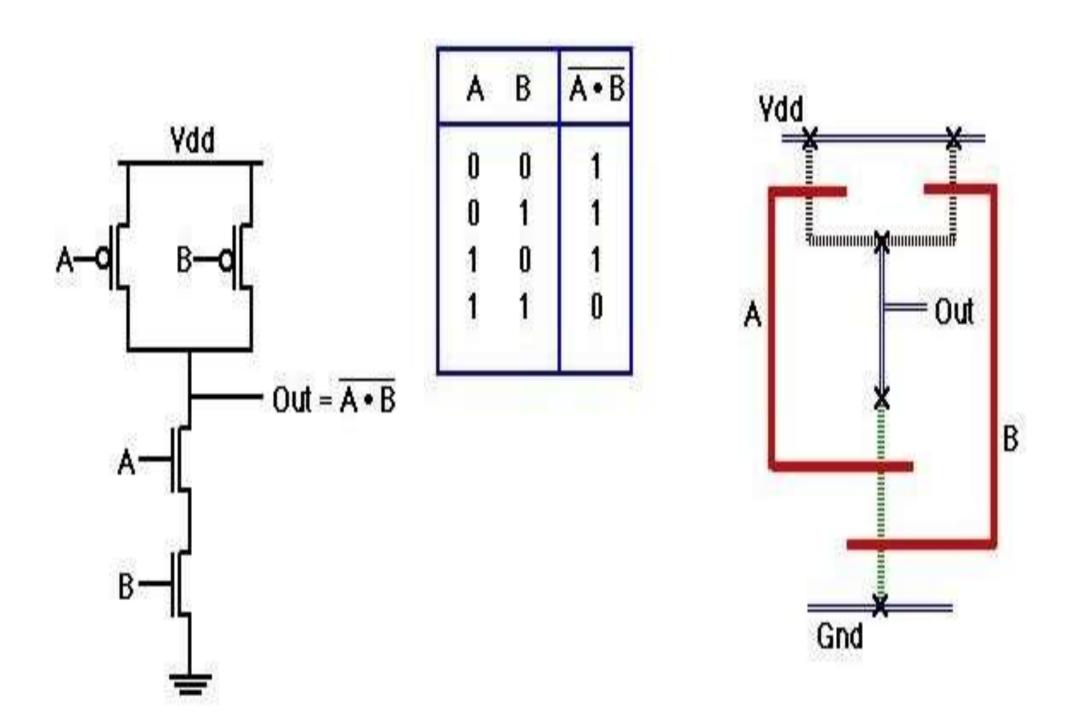

### **STATIC CMOS NAND GATE**

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

9/2/2022

--Pull Down: Connect to ground If A=1 **AND** B=1 --Pull Up: Connect to VDD If A=0 **OR** B=0

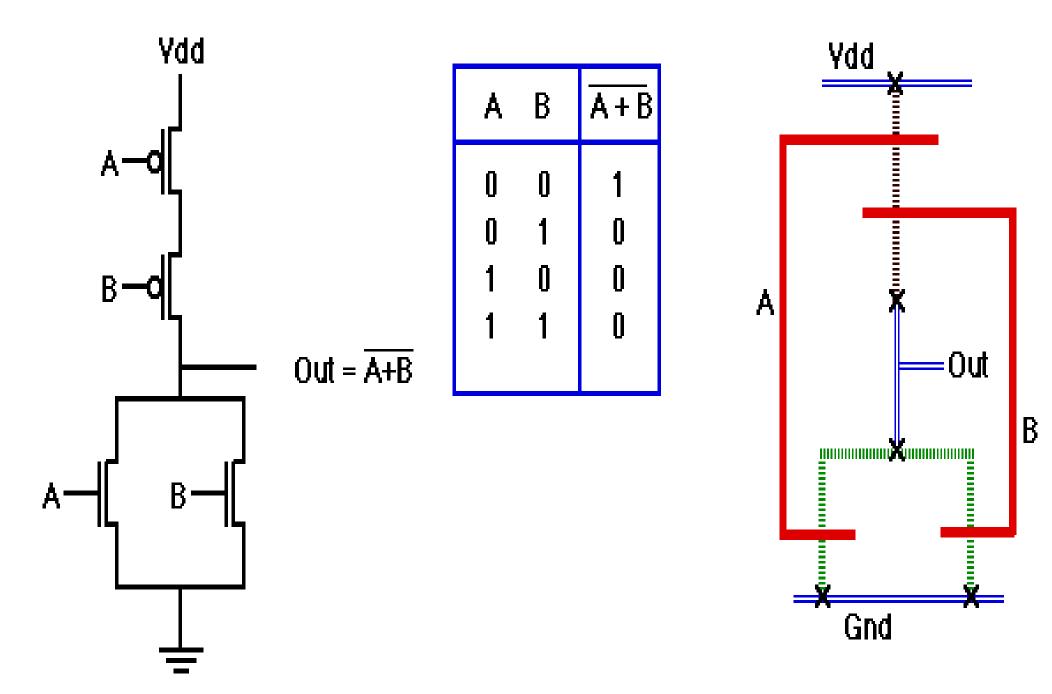

**STATIC CMOS NOR GATE**

9/2/2022

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

--Pull Down: Connect to ground If A=1 **OR** B=1 --Pull Up: Connect to VDD If A=0 AND B=0

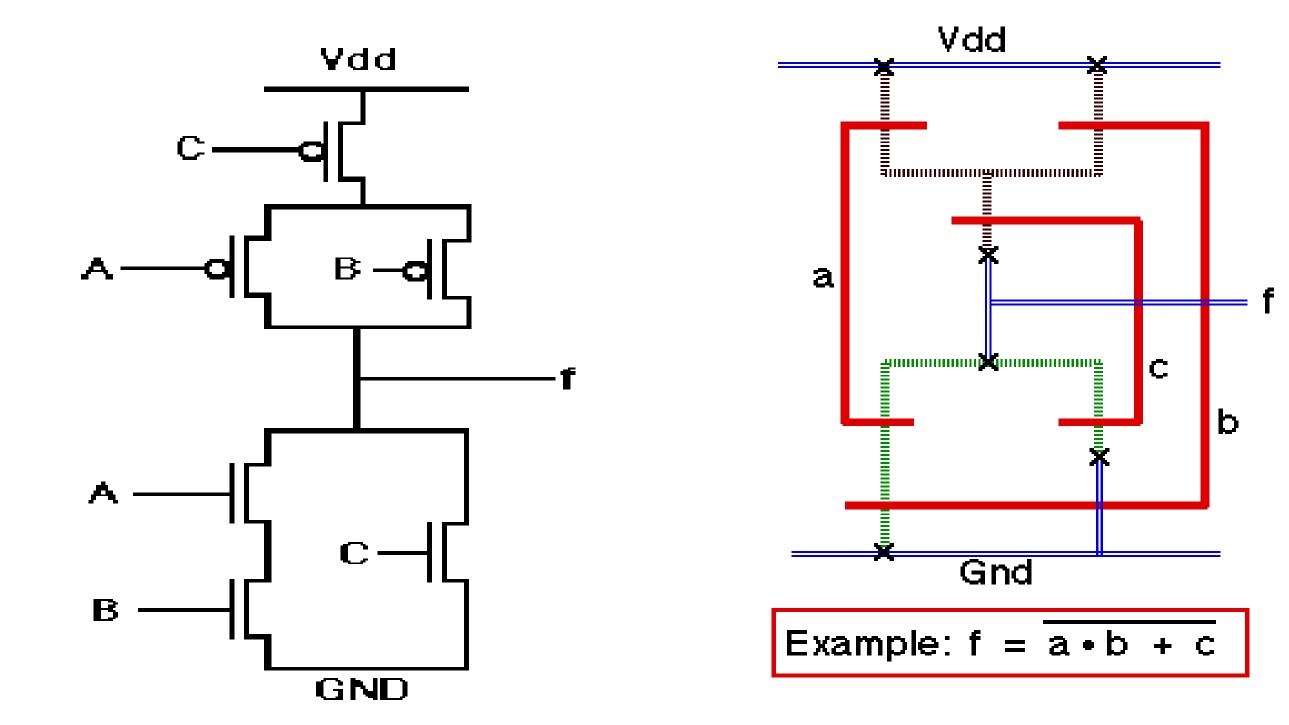

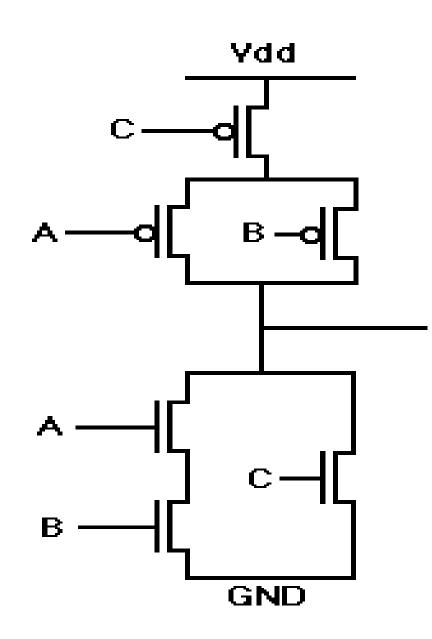

### **STATIC CMOS DESIGN EXAMPLE STICK DIAGRAM**

Example:  $f = \overline{(A \cdot B) + C}$

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

9/2/2022

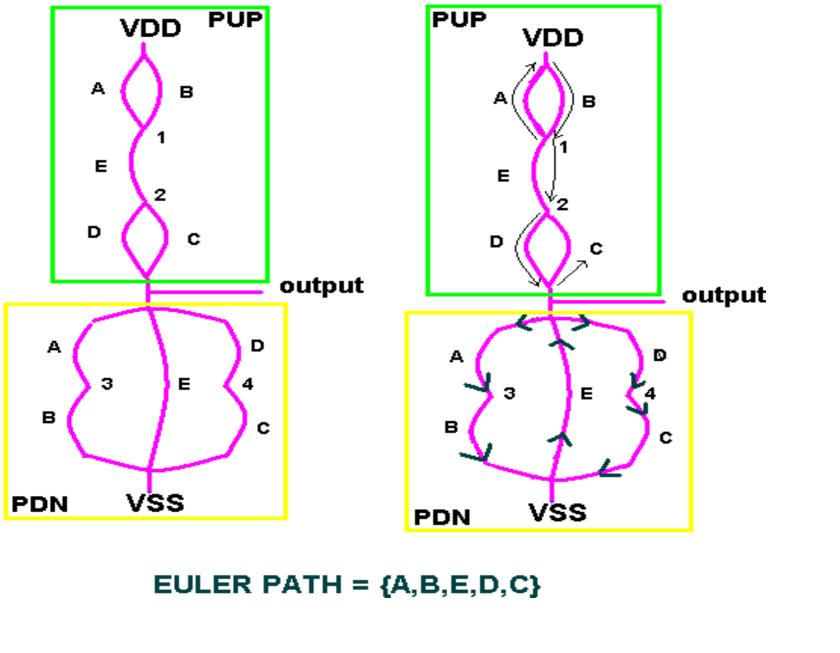

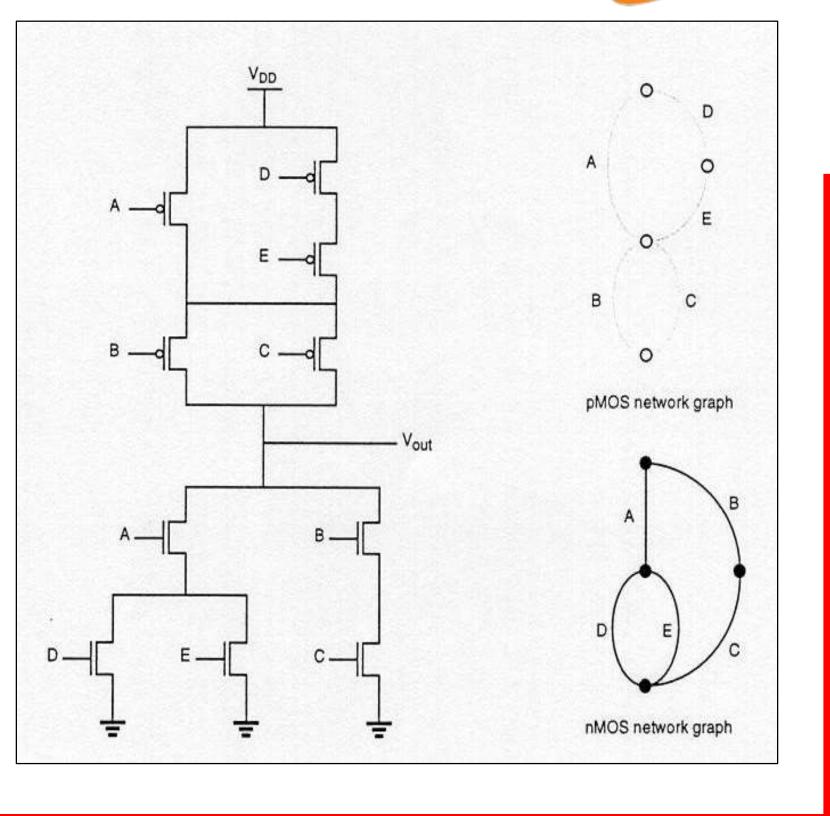

### **COMPLEX LOGIC GATES LAYOUT**

EX: F = AB + E + CDEuler paths Circuit to graph (convert) 1) Vertices are source/Drain connections 2) Edges are transistors

Find p and n Euler paths

F = (AB)+E+(CD)

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

### **CLASS ROOM ACTIVITY**

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

9/2/2022

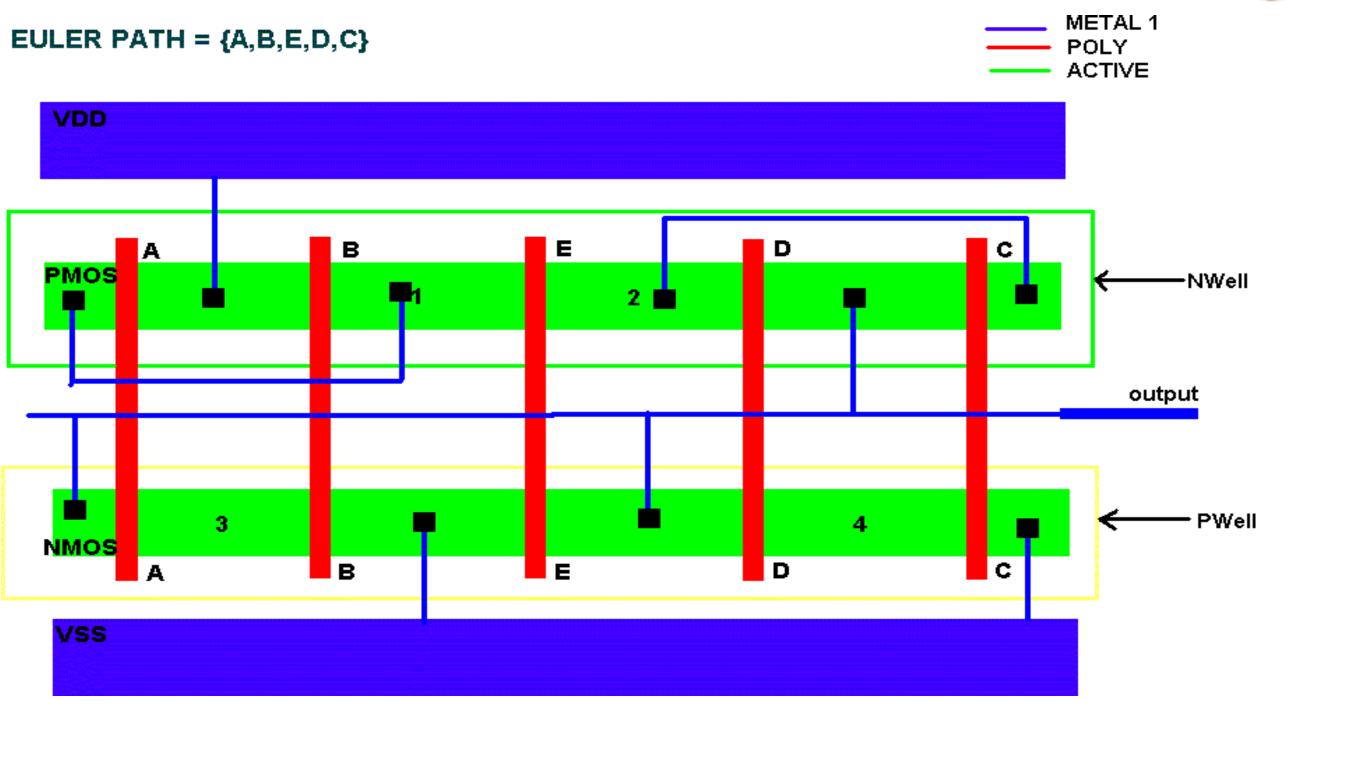

### **EULER PATH**

9/2/2022

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

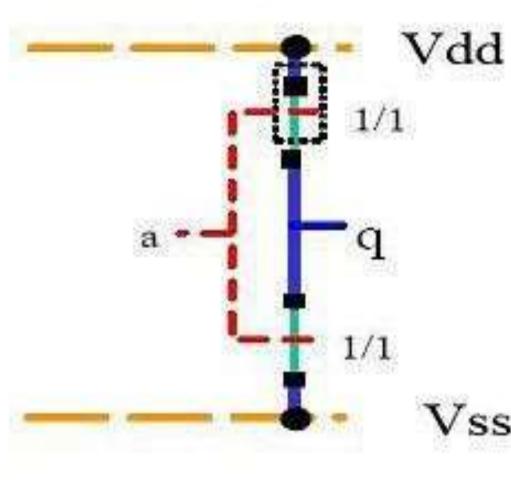

### **PMOS & NMOS**

•This notation indicates only the relative positioning of the various design components.

•The absolute coordinates of these elements are determined automatically by the editor using a compactor.

•The compactor translates the design rules into a set of constraints on the component positions, and solve a constrained optimization problem that attempts to minimize the area or cost function.

### **EULER GRAPH-STICK DIAGRAM COMPARISON**

9/2/2022

### YOUTUBE VIDEO LINK

### STICK DIAGRAM - simplified (VLSI) https://www.youtube.com/watch?v=wqRGa5sOUmc&t=212s

9/2/2022

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

### ASSESSMENT-CMOS INVERTER COLOURED STICK DIAGRAM

### 1.DRAW THE CMOS INVERTER STICK DIAGRAM 2.DRAW THE CMOS NAND GATE

9/2/2022

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT

### 3.TELL ME THE COLOR CODING NAME ?????

# **ADVANTAGE & DISADVANTAGE**

•ADVANTAGE : Designer does not have to worry about design rules, because the compactor ensures that the final layout is physically correct. •**DISADVANTAGE** : The outcome of the compaction phase is often unpredictable. The

resulting layout can be less dense than what

is obtained with the manual approach. It does

not show exact placement, transistor sizes,

wire lengths, wire widths, tub boundaries.

### **SUMMARY & THANK YOU**

9/2/2022

STICK DIAGRAM /119ECB302-VLSI DESIGN/SWAMYNATHAN.S.M/ECE/SNSCT