### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35 An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+'Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

### COURSE CODE & NAME: 16EC303 VLSI DESIGN

### III YEAR/V SEMESTER UNIT 1- MOS TRANSISTOR PRINCIPLE TOPIC 3 CMOS FABRICATION N-WELL PROCESS

N WELL /16EC202 VISI

8/29/2022

DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

## OUTLINE

- •CMOS Inverter in n-well process 1-8 steps

- •Activity

- •CMOS Inverter in n-well process 9-17 steps

- •Inverter Cross section

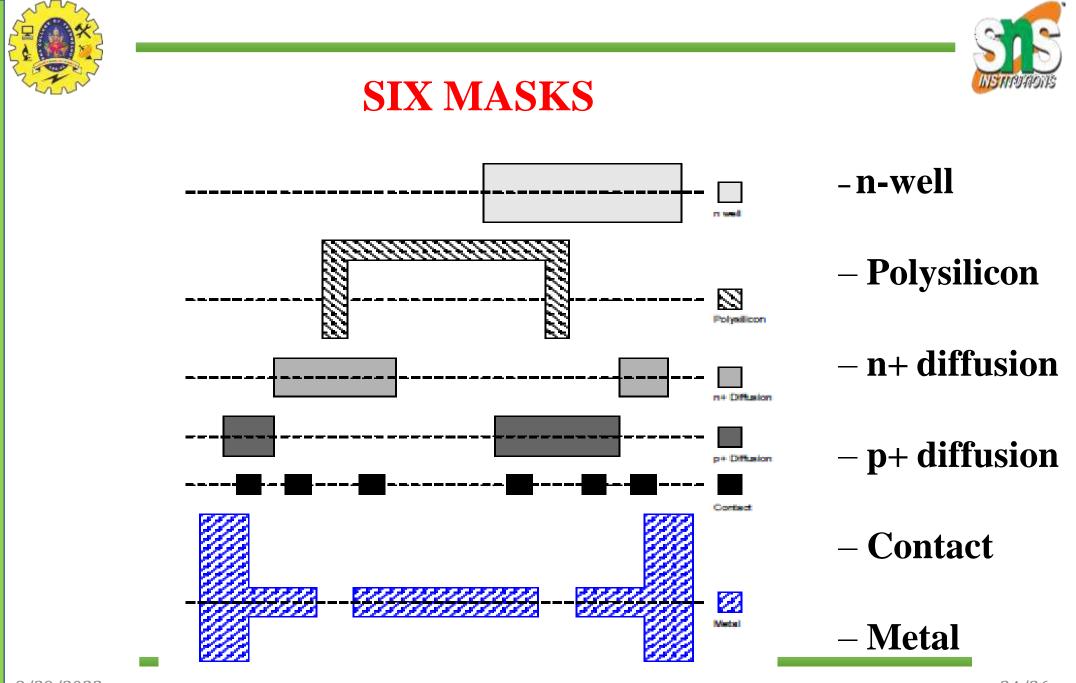

- •Mask levels

- •Assessment

- •Summary

### N-WELL VS P-WELL

# <u>n-well:</u> The pMOS transistors are placed in the n-well and the nMOS transistors are created on the substrate

### <u>P-well:</u> The nMOS transistors are placed in the pwell and the pMOS transistors are created on the substrate

## The wafer is oxidised at a high temperatureThis must be patterned to define the n-well

## The photoresist is deposited throughout the waferThe PR has to be patterned to allow formation of the well

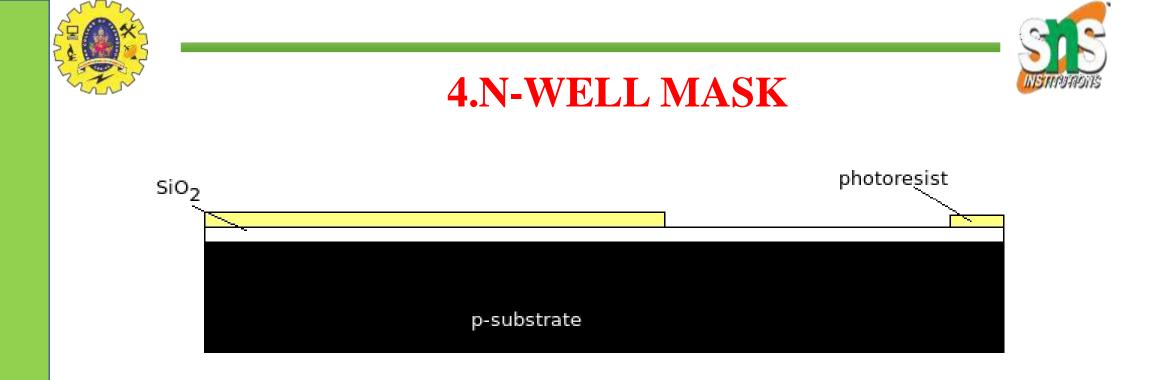

## •The PhotoResist is exposed through the n-well mask

•The softened PhotoResist is is removed to expose the oxide

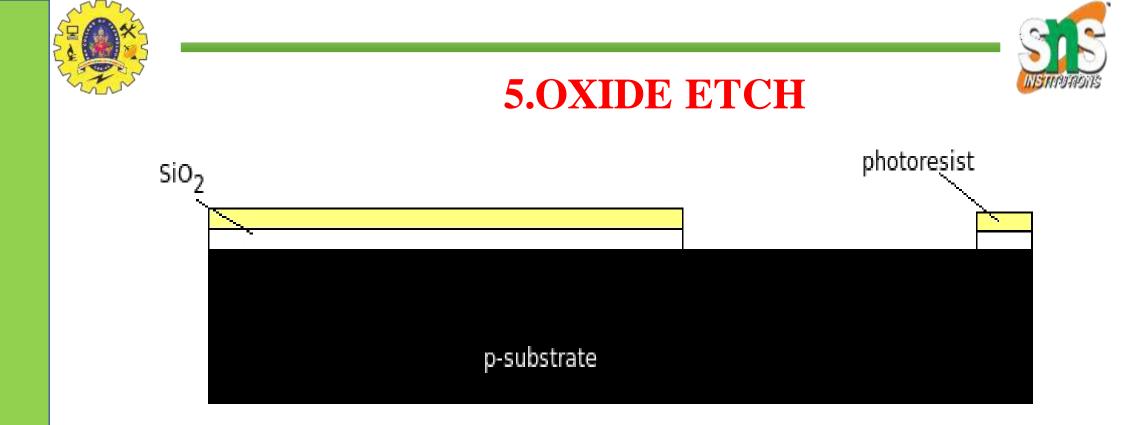

•The oxide is etched with HF acid where unprotected by Photo Resist

•The wafer is now exposed to the n-well area

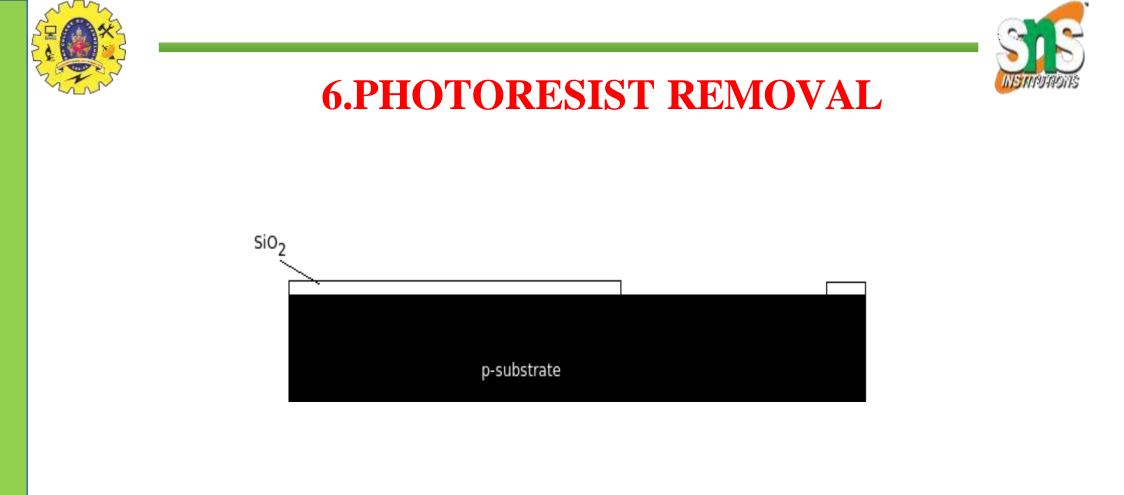

## The remaining PR is removed via piranha etchThe well is ready to be formed

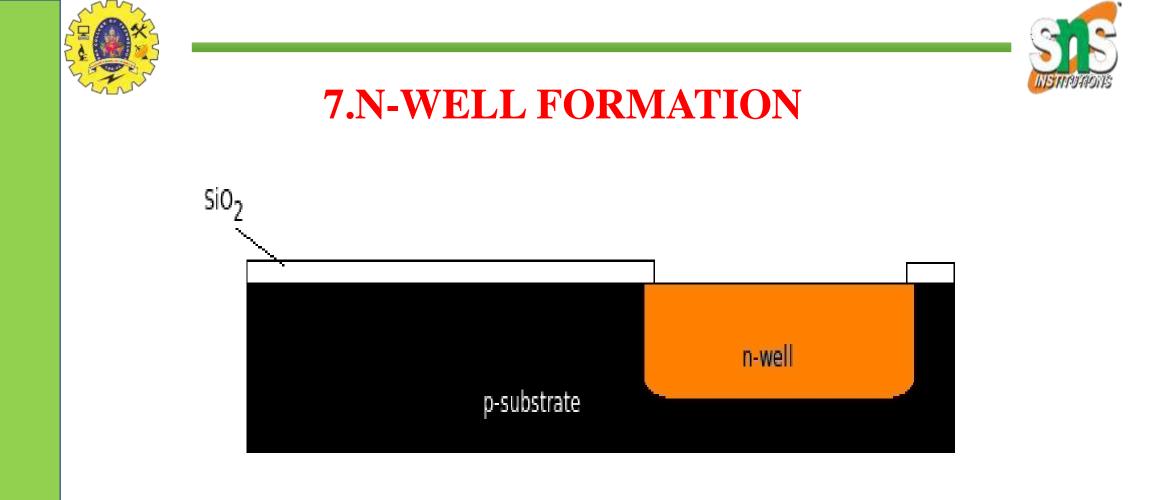

The diffusion process can make the n-wellIon implantation can also form the same

### **8.OXIDE REMOVAL**

# The remaining oxide is stripped with HF acidThis leaves the exposed wafer with the n-well formed

### Connections

## Start the word from Electronics..Next starting letter is S

N-WELL/16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

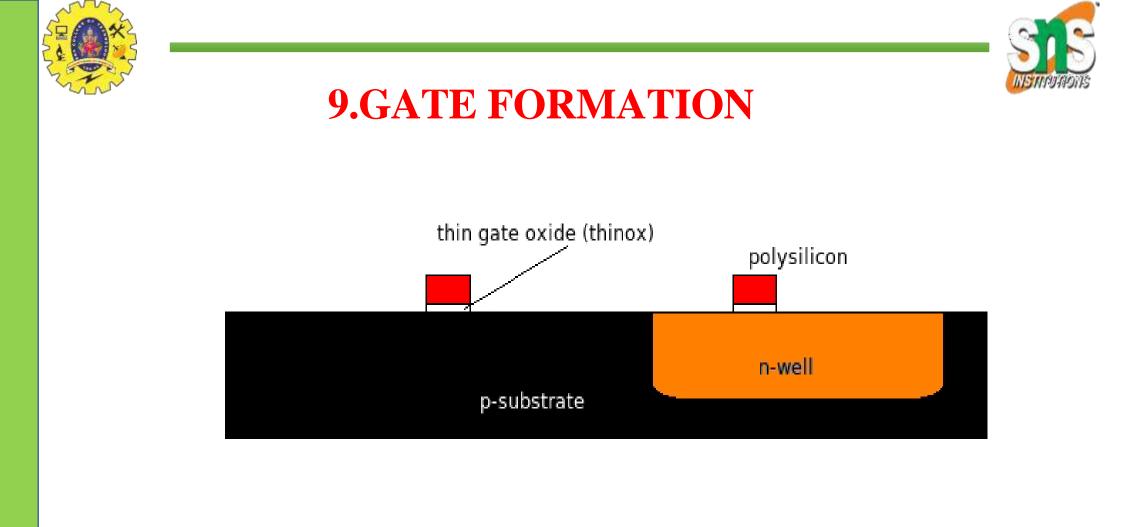

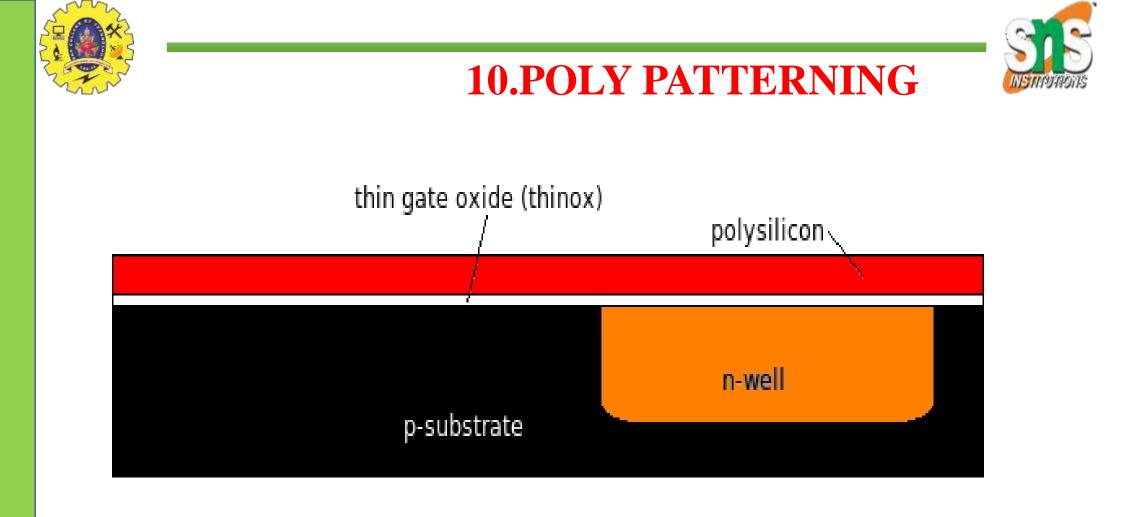

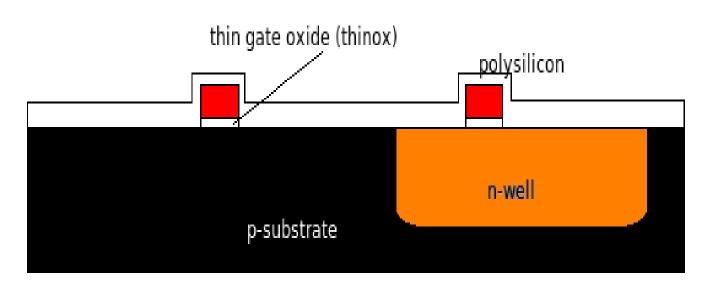

The gates are made up of polysilicon over thinoxCVD is used to grow the poly (heavily doped) layer

The wafer is now patterned with PhotoResist and the poly maskFinally this leaves the device gates

## **11.DIFFUSION PATTERN**

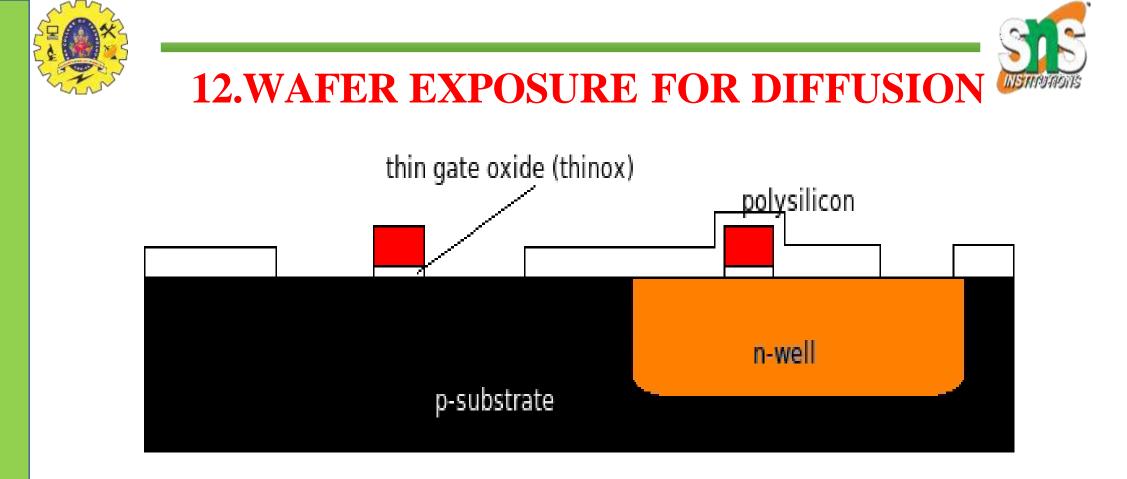

Again, a protective oxide is grown and PhotoResist deposited

PhotoResist is patterned according to the diffusion mask

# The protective oxide is etched awayThe wafer is exposed for S/D formation

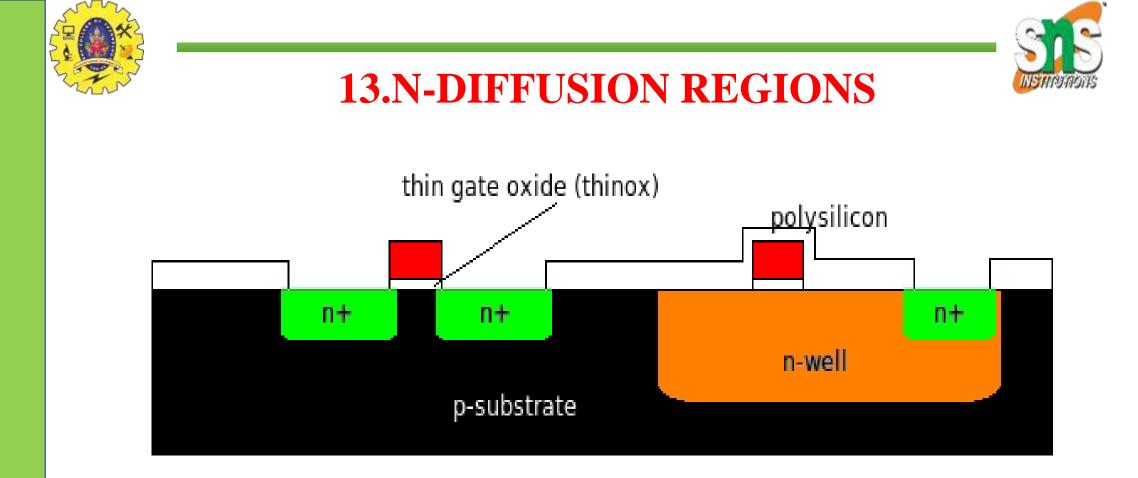

The n+ diffusion regions are formed

Polysilicon blocks the channel area

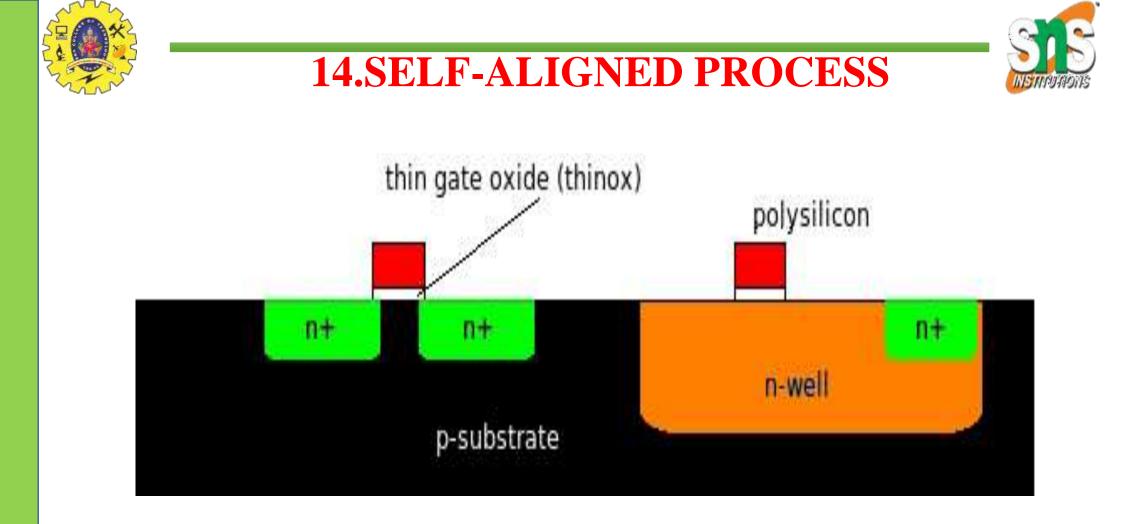

# This is a self-aligned processS/D are automatically formed adjacent to the gate

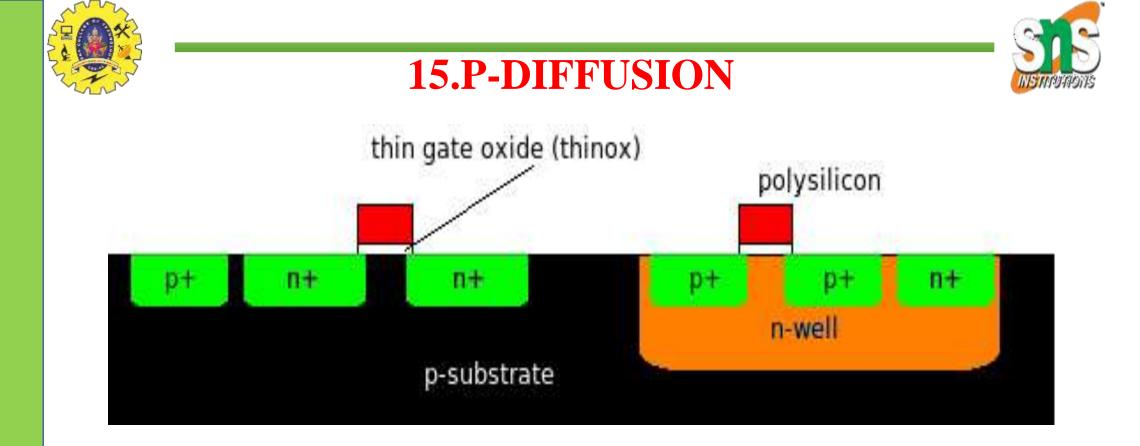

# The p-diffusion mask is used nextThis completes creation of all active regions

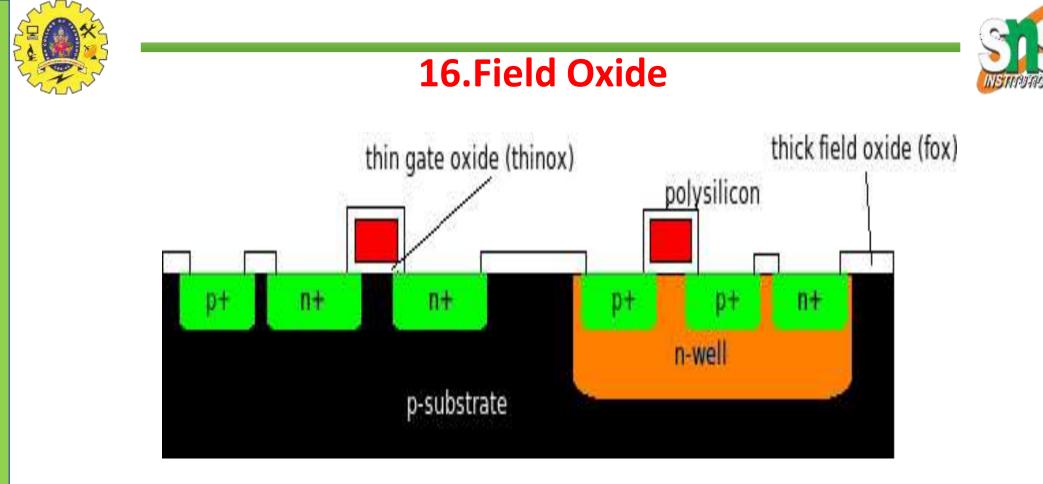

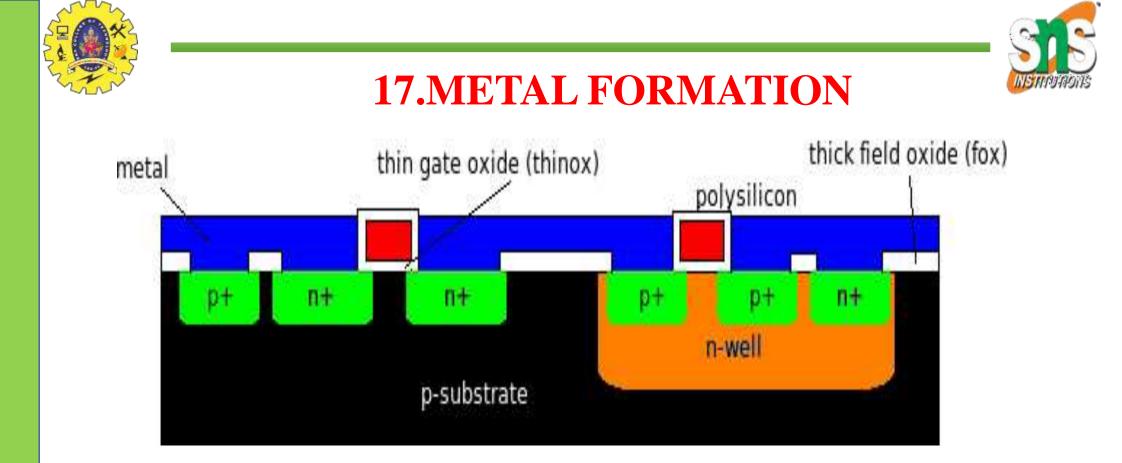

The field oxide is grown to insulate wafer and metalIt is patterned with the contact mask

Al is sputtered over the entire area filling contact cuts tooMetal is patterned with the metal mask

transistors

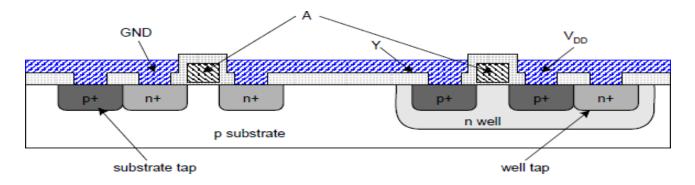

## **INVERTER CROSS-SECTION**

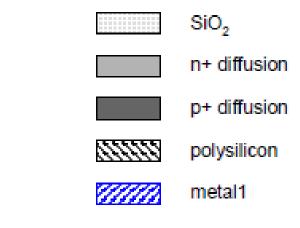

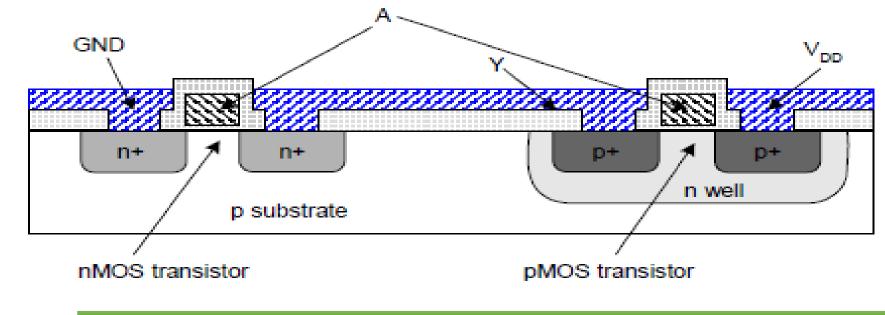

•Typically use p-type substrate for nMOS

• Requires n-well for body of pMOS transistors

- •Substrate must be tied to GND, n-well to VDD

- Use heavily doped well and substrate contacts / taps

8/29/2022

DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

24/26

1.Six masks-Fill the missed steps n-well

- ----diffusion

- -----diffusion

- Contact

- Metal

- 2. Tell me the n-well EVEN steps3. Tell me the n-well ODD steps

N-WELL/16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT